# Electronically Transparent Graphene Barriers against Unwanted Doping of Silicon

Calvin Pei Yu Wong,<sup>†,‡</sup> Terence Jun Hui Koek,<sup>‡</sup> Yanpeng Liu,<sup>‡</sup> Kian Ping Loh,<sup>‡</sup> Kuan Eng Johnson Goh,<sup>||</sup> Cedric Troadec,<sup>\*,||</sup> and Christian A. Nijhuis<sup>\*,†,‡,§,⊥</sup>

<sup>†</sup>NUS Graduate School for Integrative Sciences and Engineering, Centre for Life Sciences (CeLS), 28 Medical Drive, Singapore 117597, Singapore

<sup>‡</sup>Department of Chemistry, National University of Singapore, 3 Science Drive 3, Singapore 117543, Singapore

<sup>II</sup>Institute of Materials Research and Engineering (IMRE), Agency for Science, Technology and Research (A\*STAR), 3 Research Link, Singapore 117602, Singapore

<sup>§</sup>Graphene Research Centre, Faculty of Science, National University of Singapore, 6 Science Drive 2, Singapore 117546, Singapore <sup>⊥</sup>Solar Energy Research Institute of Singapore (SERIS), National University of Singapore, Block E3A, 7 Engineering Drive 1, Singapore 117574, Singapore

## **Supporting Information**

**ABSTRACT:** Diffusion barriers prevent materials from intermixing (e.g., undesired doping) in electronic devices. Most diffusion barrier materials are often very specific for a certain combination of materials and/or change the energetics of the interface because they are insulating or add to the contact resistances. This paper presents graphene (Gr) as an electronically transparent, without adding significant resistance to the interface, diffusion barrier in metal/semiconductor devices, where Gr prevents Au and Cu from diffusion into the Si, and unintentionally dope the Si. We studied the electronic properties of the *n*-Si(111)/Gr/M Schottky barriers (with and without Gr and M = Au or Cu) by I(V) measurements and at the nanoscale by ballistic electron emission spectroscopy (BEEM). The layer of Gr does not change the Schottky barrier of these junctions. The Gr barrier was stable at 300 °C for 1 h and prevented the diffusion of Cu into *n*-Si(111) and the formation of Cu<sub>3</sub>Si. Thus,

we conclude that the Gr is mechanically and chemically stable enough to withstand the harsh fabrication methods typically encountered in clean room processes (e.g., deposition of metals in high vacuum conditions at high temperatures), it is electronically transparent (it does not change the energetics of the Si/Au or Si/Cu Schottky barriers), and effectively prevented diffusion of the Cu or Au into the Si at elevated temperatures and vice versa.

KEYWORDS: graphene, diffusion barrier, BEEM, copper, gold, silicon, electronically transparent

## INTRODUCTION

Controlling the properties of metal-semiconductor interfaces is important because they determine whether, for instance, metal-semiconductor contacts are ohmic or not, or control contact resistance. Diffusion of metals into Si may cause unwanted doping and the formation of deep level traps.<sup>1,2</sup> Protective layers that minimize interfacial diffusion in general change the electronic properties of the interfaces they protect.<sup>3</sup> For instance, in microelectronics Cu, W, or Al, diffusion into Si is minimized by using TaN or TiN barriers,<sup>4-8</sup> which are more resistive than the typical interconnect metals, resulting in an increase of power consumption and increased resistivecapacitance delay.<sup>9</sup> In commercial Si-based solar cells, diffusion barriers are avoided by simply using expensive Ag topelectrodes because Ag diffuses slowly into Si relative to the lifetime of the solar cells.<sup>10,11</sup> An "ideal" barrier should fulfill three requirements: the barrier must be (i) impermeable to metal atoms/ions, (ii) mechanically and thermally stable during the fabrication conditions (high vacuum and temperatures

(typically up to 1000  $^\circ C)$ ), and (iii) electronically transparent (does not affect the electronic properties of the interface it protects).

We propose to use graphene as a protection barrier against metal diffusion for the following five reasons. (i) It is impermeable to gases<sup>12</sup> and metal atoms.<sup>13</sup> (ii) It has no band gap<sup>14</sup> and forms ohmic contact with most metals. (iii) It is atomically thin and electrons tunnel through the graphene barrier layer easily.<sup>15,16</sup> (iv) It has great mechanical stability with a Young's modulus of 1 TPa.<sup>17</sup> (v) It is chemically stable, has high thermal conductivity<sup>18</sup> and it can withstand thermal stressing up to 400 °C in air,<sup>19</sup> and estimated up to 2300 °C in vacuum.<sup>20</sup> Here we describe the use of graphene (Gr) as a protective barrier for hydrogen passivated *n*-Si(111)/Cu and *n*-Si/(111)Au structures. We found that the barrier height of

Received:September 4, 2014Accepted:October 20, 2014Published:October 20, 2014

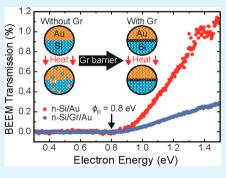

**Figure 1.** (a) Schematic of the STM/BEEM apparatus and the *n*-Si(111)/Gr/Au device with and without the Gr protective barrier and the corresponding energy level diagram (b), the base contact in (a) serves as a common contact for ground in BEEM measurements or to apply a bias in I(V) measurements.

these Schottky barriers were not altered by the presence of the Gr layer, no metal atoms diffused into the Si layer (within detection limits), and the Gr protective barrier withstood the harsh fabrication conditions. From this experiment, we conclude that Gr is an electronically transparent protective barrier and blocks unwanted doping at the atomic level.

Often the fabrication of a well-defined interface is troublesome because during the fabrication steps (that often require high temperatures and high-vacuum conditions, etching, or chemical and mechanical cleaning steps) the materials at the interface may be damaged, or diffuse into one and another." Figure 1a shows schematically a damaged interface where one material diffused into the other and an "ideal" interface where diffusion is avoided by a protective barrier. These protection layers often add to the contact resistance (and higher power consumption),9 and change the interface energetics, which impact device behavior. Often these protection layers have been optimized for certain specific applications.<sup>4-8</sup> TaN,<sup>4</sup> Ta,<sup>7</sup> or bilayer TaN/Ta8 barriers prevent the diffusion of Cu into Si and low  $\kappa$  dielectrics for Cu metallization, or TiN<sup>5,6</sup> for W/Al metallization. Existing protective barriers change the electronic properties of the interface due to the differences in work functions of the different materials. For instance, TaN forms a Schottky barrier of 0.48 eV with *n*-type silicon and 0.68 eV with *p*-type silicon,<sup>21</sup> TiN forms a Schottky barrier of 0.55 eV with *n*type silicon and 0.57 eV with *p*-type silicon.<sup>22</sup> These differences in the Schottky barrier heights result in drastic changes to the energetics of the interfaces complicating the design and fabrication process.

Ag, Cu, and Au are widely used as interconnects in electronic devices, as they have the highest electrical conductivities amongst metals.<sup>23</sup> Except for Ag, which does not diffuse significantly into Si relative to the lifetime of the devices at low temperatures,<sup>10,11,24</sup> Cu and Au diffuses readily into Si: the interstitial hopping energy of Cu is only 0.18 eV and the diffusion coefficient of Cu in Si is  $2.84 \times 10^{-7}$  cm<sup>2</sup> s<sup>-1</sup> at 300  $K_{r}^{25}$  which is 4 orders of magnitude higher than that of Au<sup>26</sup> and 7 orders of magnitude higher than that for Ag.<sup>11</sup> This means that at 300 K, Cu can diffuse across the whole thickness of a standard 500-600  $\mu$ m Si wafer in a few hours. The diffusion barrier for the current 22 nm technology is about 3 nm thick TaN, which prevents diffusion of Cu into Si.<sup>27</sup> The drive for device miniaturization of microelectronic components also includes reducing the thickness of the protective barriers to minimize resistance and power loses.<sup>9</sup> Reducing the resistivity by reducing the thickness is an obvious strategy to reducing resistances, but the barrier performance decreases with decreasing thickness. The resistivity of TaN is about a factor of 10 to 100 higher than Cu, depending on the deposition conditions, stoichiometry, and phases.<sup>28</sup> Although subnanometer TaN barriers have been demonstrated by atomic layer deposition (ALD),<sup>29</sup> these films tend to be highly resistive, expensive, and difficult to scale up, and thus are not ideal for use in interconnects. Hence, a monatomic thin layer that effectively blocks diffusion without adding significant resistance is required to further down-size microelectronics.<sup>30,31</sup>

This paper describes the properties of the buried n-Si(111)/ Gr/metal interfaces using ballistic electron emission microscopy (BEEM) and current-voltage I(V) measurements. Figure 1 shows the energy level diagram and illustrates how BEEM can be used to determine the Schottky interface heights of a buried interface with nanometer spatial resolution.<sup>32,33</sup> Ballistic electrons emitted from an STM tip probe the buried Schottky interface of a metal/semiconductor interface. In BEEM experiments, electrons are injected into a thin metal base, i.e., the thin (here 15 nm) gold layer in Figure 1a, from the STM tip by applying a negative tip bias, while the metal base and the semiconductor substrate are grounded. A portion of these electrons are not scattered, the ballistic electrons, as they travel through the metal base to reach the metal-semiconductor Schottky interface and subsequently they are collected as the BEEM current at the backside of the semiconductor if they have enough energy to overcome the Schottky barrier  $(\phi_{

m B})$  and fulfill the momentum conservation rules.<sup>32,33</sup> The BEEM current is a function of the bias applied between the tip and the metal base. Because the lateral position of the STM tip can be controlled with atomic scale precision, the BEEM response can be mapped with typically nanometer scale resolution.<sup>33</sup>

Graphene has been used as protection barriers before in oxidation resistant coatings,<sup>34</sup> molecular electronics,<sup>35</sup> metal diffusion barriers,<sup>13,30,31</sup> and other applications.<sup>36</sup> Nguyen et al.<sup>30</sup> reported using trilayer graphene as a Cu diffusion barrier for applications in microelectronics and Hong et al.<sup>31</sup> reported using monolayer graphene as a Cu diffusion barrier. However, the electronic behavior of the graphene barrier layer in semiconductor/graphene/metal devices have not been characterized thoroughly. Here we use BEEM and I(V) measurements to show that Gr is a promising material to protect barriers at the nanoscale while introducing negligible resistance and does not change the energetics of the interface. Our findings are important because graphene can be used to prevent incompatible materials from diffusing into one another without changing the electrical properties of the interface (electronically transparent). We postulate that the electronic transparency of the graphene barrier is important in applications where unwanted doping must be avoided without introducing significant resistance.37-40

#### EXPERIMENTAL DETAILS

**Fabrication of the Si/Gr/Metal Structures.** The *n*-type silicon (111) wafers (1–10  $\Omega$ , phosphorus doped) were purchased from Syst Integration, diced into 6 × 6 mm, and used as the semiconductor substrate. Prior to Schottky metal or graphene deposition, the silicon wafers were cleaned by 1 min sonication in acetone (CMOS grade, J.T. Baker) and isopropyl alcohol (CMOS grade, J.T. Baker), to remove organic contaminants followed by a brief etch in buffered hydrofluoric acid (Honeywell (7:1) Buffered Oxide Etchant) for 60 s to remove the native SiO<sub>2</sub> layer and to form a hydrogen passivated surface.<sup>41</sup>

Monolayer graphene on Cu (Bluestone Global Tech) was transferred using a previously reported wet transfer process.<sup>42</sup> We spin coated a layer of PMMA of ~200 nm (A4 495k, MicroChem Corp; at 2500 rpm for 40 s) on Gr on Cu followed by a 80 °C bake for 15 min to remove residual solvents. The PMMA film functions as the support in the transfer process. The graphene on the backside of the copper foil was removed in O<sub>2</sub> plasma (50 W, 15 min, 0.5 mbar). The 25  $\mu$ m thick Cu substrate was then etched away by floating the Cu/Gr/PMMA stack in an aqueous solution of ammonium persulfate (Alfa Aesar; 10 wt % solution in deionized water) for 3 h. The Gr/PMMA stack was washed by repeated transfer onto copious amounts (5 × 1 L) of deionized water using an oxygen plasma treated Si wafer before transferring onto a freshly prepared hydrogen passivated silicon surface and dried naturally in the clean room environment.

Metal deposition was carried out in a thermal evaporator (R-DEC co. UNS021) with  $<5 \times 10^{-7}$  mbar base pressure using Au (99.99%; Advent Research Materials) or Cu (99.999%; Advent Research Materials) in a tungsten boat (Kurt J. Lesker). We deposited a layer of 15 nm of Au, or 100 nm of Cu, at 0.2 Å/s, monitored using a quartz crystal balance (Inficon XTM/2), through a shadow mask containing a  $5 \times 5$  array of 0.5 mm diameter circular holes in a 100  $\mu$ m thick stainless steel sheet. The device area was determined by scratching the graphene using a sharp tweezer between the 0.5 mm diameter Au or Cu dots to prevent leakage currents due to the high conductivity of graphene in the *xy*-plane.

Electrical Characterization. The I(V) and STM/BEEM<sup>32,33</sup> measurements were carried out with a home-built STM/BEEM setup (Figure 1a); the details of this setup have been described elsewhere.4 <sup>b</sup> Briefly, a thin gold wire (50  $\mu$ m) held by a high precision manipulator (Kleindiek Nanotechnik) was used to ground the Au base electrode for BEEM measurements or to apply a bias during I(V)measurements. An ohmic back contact, made by scratching the native oxide layer and depositing Ag (99.999%; Advent Research Materials) or eutectic Ga-In (Sigma-Aldrich), to the semiconductor was connected to a high gain amplifier (FEMTO DHPCA-100) and used as a current collector for BEEM measurements or as the drain in I(V) measurements. The STM/BEEM measurements were all conducted in air and at ambient temperature using mechanically cut Pt-Ir tips on an Agilent STM head and controlled with a Nanonis STM controller.<sup>43</sup> Thermal stressing of the n-Si(111)/Cu device was carried out in a high vacuum chamber ( $<5 \times 10^{-7}$  mbar) equipped with a feedback controlled sample stage heater. The sample temperature was raised slowly (2.5 °C/min) from room temperature to the desired temperature, holding for 1 h, and then cooled to room temperature by switching off the heater in the vacuum chamber. The I(V) measurements were carried out in a Materials Development Corp (MDC) CV-IV Measuring System from -0.5 to 1 V with a step size of 7.5 mV and 0.1 s hold time.

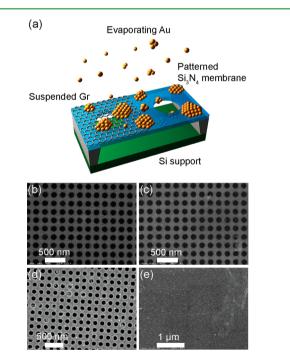

**Suspended Graphene.** We fabricated an array of holes with a diameter of 100 nm by electron-beam lithography (Elionix ELS-7000) and reactive ion etching (RIE) (Plasmalab 80, Oxford) in a 100 nm thick Si<sub>3</sub>N<sub>4</sub> membrane following a previously published procedure.<sup>44</sup> Briefly, a 170 nm thick ZEP-520A resist was spin-coated onto a 100 nm thick Si<sub>3</sub>N<sub>4</sub> membrane substrate and the material was baked at 180 °C for 2 min. Designed patterns (array of 100 nm diameter circles) were exposed at a dose of 300  $\mu$ C/cm<sup>2</sup> by using an electron beam with an acceleration voltage of 100 kV and beam current of 50 pA. The exposed samples were developed in *o*-xylene for 30 s and rinsed in isopropyl alcohol (IPA) for 20 s. The resist patterns were transferred

to the Si<sub>3</sub>N<sub>4</sub> membrane layer by RIE in a mixture of CHF<sub>3</sub> (55 sccm) and O<sub>2</sub> (5s sccm) at 0.1 mbar at a power of 175 W for 3 min. The resist was removed in microposit 1165 remover (MicroChem Corp), and the substrates were rinsed with IPA and deionized water and blown dry with nitrogen gas. Onto these holes we transferred Gr followed by thermal deposition of Au (30 nm) using procedures described above. We imaged the structures by SEM (Elionix ESM-9000) using an acceleration voltage of 5 kV for Si<sub>3</sub>N<sub>4</sub> to reduce charging effects and 30 kV when coated with Au.

**Raman and Atomic Force Microscopy.** We characterized graphene using a commercial Witec alpha 300R Raman system with a 532 nm laser (2.33 eV) excitation source. We kept the laser power below 3 mW to avoid laser-induced damage to graphene.<sup>45</sup> A 100× objective lens with a numerical aperture (N.A.) of 0.90 was used to focus the laser spot to about 1  $\mu$ m in diameter during the Raman measurements. Typical integration time for spectrum acquisition is 5 s for graphene on SiO<sub>2</sub> (280 nm) and 10 s for graphene on Si(111)-H surfaces. Atomic force microscopy images of graphene were recorded in tapping mode (Bruker Dimension Fastscan) using FastScan-A probes (resonant frequency, 1.4 MHz; force constant, 18 N/m).

**X-ray Diffraction.** We characterized Cu<sub>3</sub>Si formation in *n*-Si(111)/ Cu devices using a commercial Bruker D8 general area detector diffraction system (GAADS) equipped with a two-dimensional (2D) detector and Cu K $\alpha$  radiation ( $\lambda = 0.154$  nm). We recorded the Debye diffraction pattern using the 2D detector from 2 $\theta$  angle (*x*-axis) of 20° to 85° and integrated the signal over the sample tilt angle  $\chi$  (*y*-axis). The strong Si(111) substrate peak at 28° is avoided in the scan to prevent detector overloading.

#### RESULTS AND DISCUSSION

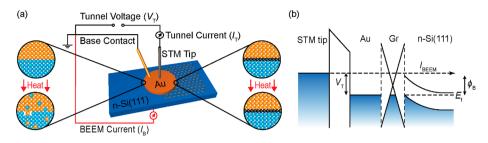

Fabrication. We fabricated n-Si(111)/Gr/Au devices by transferring Gr using a wet transfer process onto hydrogen passivated Si(111) using well-established methods<sup>42</sup> followed by Au deposition. As graphene is not visible by the eye on hydrogen passivated Si substrates,<sup>46</sup> we used optical microscopy to characterize the quality of the Gr from the same batch of Cu/Gr by transferring graphene on 280 nm SiO<sub>2</sub> substrates and measured atomic force microscopy (AFM), and Raman spectroscopy on both 280 nm SiO<sub>2</sub> and hydrogen passivated substrates. Figure 2 shows the results from which we make the following observations. (i) The optical micrographs show that the entire Si surface was covered with a Gr layer (with some PMMA residues)<sup>47</sup> and a few islands of bilayer and multilayer Gr, but no cracks were visible. (ii) The AFM images show typical defects such as PMMA residues, wrinkles, and folds, but no cracks. (iii) The Raman spectra show that the ratio of  $I_{2D}/I_{G}$ is ~2 and the width of the  $2D_{monolayer}$  peak is ~27  $cm^{-1}$  for monolayer graphene, and the  $I_{2D}/I_{G}$  ratio is ~0.9 and the width of the  $2D_{bilayer}$  peak is about ~46 cm<sup>-1</sup> for bilayer graphene.<sup>45</sup> The Raman spectra show a small D peak (about 10 times smaller in intensity that the G peak), which is associated with islands of bilayer graphene. From these data, we conclude that we successfully transferred continuous films of Gr similar in quality as previously reported layers.<sup>45,48</sup>

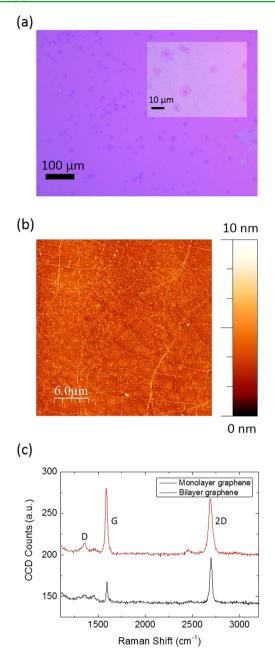

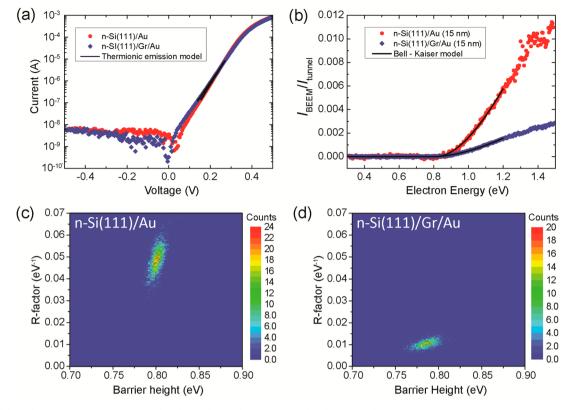

**Electronic Properties.** Figure 3 shows the I(V) measurements and the ballistic electron emission spectroscopy (BEES) plots<sup>49</sup> of the *n*-Si(111)/Au and the *n*-Si(111)/Gr/Au devices both with 15 nm of Au. We fitted the I(V) curves (forward bias; solid black lines in Figure 3a) to the simplified thermionic emission model (see the Supporting Information) to determine the Schottky barrier height ( $\phi_{\rm B}$ ) and ideality factor (*n*) as follows.<sup>2</sup>

$$I \approx \left[ AA^{**}T^{2} \exp\left(\frac{-q\phi_{\rm B}}{k_{\rm B}T}\right) \right] \left[ \exp\left(\frac{qV_{\rm D}}{nk_{\rm B}T}\right) \right]$$

(1)

**ACS Applied Materials & Interfaces**

**Figure 2.** (a) Optical micrographs of Gr on 280 nm  $SiO_2$ , (b) AFM images of Gr on *n*-Si(111)-H, and (c) Raman spectra recorded on Gr on *n*-Si(111)-H on an area with monolayer and bilayer graphene.

where q is the electric charge (=1.602 × 10<sup>-19</sup> C),  $V_D$  the voltage applied across the diode,  $k_B$  the Boltzmann constant (=1.381×10<sup>-23</sup> m<sup>2</sup> kg s<sup>-2</sup> K<sup>-1</sup>), T the absolute temperature, A the area of the diode,  $A^{**}$  (=1.12 × 10<sup>6</sup> A m<sup>-2</sup> K<sup>-2</sup>) the effective Richardson constant of *n*-type Si, and  $\phi_B$  the Schottky barrier height. Fitting the slope of the forward biased I(V) curve in the region of  $3k_BT < V < 5k_BT$  gives *n*, and the intercept of the curve with the *y*-axis gives the value of  $\phi_B$  (eq 1). We obtained  $\phi_B = 0.80$  and 0.78 eV for the devices without (with n = 1.08) and with a layer of Gr (with n = 1.20), respectively, similar to previously reported values.<sup>50</sup> From these results, we conclude that on the macroscopic scale, the presence of Gr does not significantly change the electronic properties of the *n*-Si(111)/Au Schottky interface.

Figure 3b shows the BEEM spectra that were obtained as follows. We normalized the transmission of the interface by taking the ratio of the BEEM current  $(I_{\text{BEEM}})$ , the current that flows through the Schottky interface (between the Au metal base and the n-Si(111) substrate), and the tunnel current  $(I_{\text{tunnel}})$ , the current that flows between the STM tip and the grounded Au metal base (Figure 1). We plotted this ratio vs the electron energy (eV), which is the bias between the tip and the base  $(V_{\rm T})$ . To this so-called BEES spectrum, we fitted the Bell-Kaiser model<sup>33</sup> (eq 2) to determine the local value of  $\phi_{\rm B}$  (with a spatial resolution of  $\sim 1 \text{ nm}^2$ ) and the transmission attenuation factor (R). Noisy data that falls below the statistical goodness of fit value of 0.8 were rejected (typically the noisy data come from instrumental noise). We repeated this procedure 900 times over an area of  $256 \times 256$  nm<sup>2</sup> and plotted the results in a 2D graph of R vs  $\phi_{\rm B}$  (Figure 3c,d), which serves as a unique "BEES fingerprint" of the interface.

$$\frac{I_{\text{BEEM}}}{I_{\text{tunnel}}} = R \frac{(\text{eV} - \phi_{\text{B}})^2}{\text{eV}}$$

(2)

We found that the nanoscopic values of  $\phi_{B,BEEM,n-Si(111)/Au} = 0.80 \pm 0.01 \text{ eV}$  and  $\phi_{B,BEEM,n-Si(111)/Gr/Au} = 0.78 \pm 0.01 \text{ eV}$  obtained in BEEM (Figure 3c,d) are essentially identical within the thermal broadening limit of  $3k_BT$ , i.e., the Schottky barrier heights were unchanged by the presence of Gr at the interface. The presence of the layer of Gr is apparent in the factor *R*: by modifying the *n*-Si(111)/Au interface with Gr, the value of *R* decreased from 0.05 to 0.01 eV<sup>-1</sup>. The decrease in *R*-factor shows that there is no direct contact between gold and silicon due to increased scattering of ballistic electrons at the *n*-Si(111)/Gr/Au interfaces<sup>S1</sup> and graphene is essentially "electronically transparent" because it does not change the barrier height of the *n*-Si(111)/Au system.

We explain the behavior of the buried Gr layer as follows. It is well-known that charge transfer can occur between graphene and the surface it is immobilized on.<sup>52</sup> We postulate that the Fermi level of Gr shifts toward that of the Au it interacts with, but that the Schottky-barrier height did not change because the doping level of the n-Si(111) was not changed. In other words, we postulate that the Schottky-Mott model applies.<sup>2</sup> By considering the density of states of electrons at the Fermi level of Au ( $\sim 10^{22}$  cm<sup>-3</sup>), which is several orders of magnitude above the density of states in Gr (Dirac cone linear dispersion of Gr implies that the density of states diminishes close to the intrinsic work function of  $\sim 4.6 \text{ eV}$ ),<sup>53</sup> the transfer of electrons from Au into Gr will effectively dope Gr and results in Fermi level alignment.<sup>52</sup> Further electron transfer from the *n*-type semiconductor to the Au-doped Gr (causing band bending in the semiconductor) renders Gr electronically transparent and the Schottky barrier height unchanged. 54,55 A similar explanation has been used to explain the behavior of Gr on Au showing significant *p*-doping of graphene, with a Fermi level shift of 0.35-0.4 eV<sup>54</sup> and graphene on Pt(111) showing pdoping with a Fermi level shift of 0.30 eV.<sup>56</sup>

Although the Schottky–Mott model does not take into account the semiconductor interface states that may cause Fermi level pinning, we assume that surface states of Si interact with graphene in a similar manner they interact with Au. As the surface states are an intrinsic property of the semiconductor,<sup>57</sup> it was not changed in our experiment and does not affect our overall interpretation of the Schottky barrier.

**Figure 3.** (a) I(V) measurements of the *n*-Si(111)/Au (15 nm) and the *n*-Si(111)/Gr/Au (15 nm) interfaces. The solid lines represent fits to the thermionic emission model eq 1. (b) BEEM spectra obtained for the *n*-Si(111)/Au (15 nm) and the *n*-Si(111)/Gr/Au (15 nm) interfaces. The solid lines represent fits to Bell–Kaiser model eq 2.<sup>33</sup> Dual parameter BEES plots<sup>49</sup> of *R*-factor against  $\phi_{\rm B}$  of (c) *n*-Si(111)/Au and (d) *n*-Si(111)/Gr/Au devices.

**Mechanical Stability.** In addition to electronic transparancy, the mechanical strength of the barrier determines the stability of the protection barrier during the fabrication process of the devices. Measurements of the mechanical strength of graphene by AFM nanoindentation revealed that graphene is the strongest material measured so far, with a Young's modulus of 1 TPa,<sup>17</sup> and that the mechanical strength of polycrystalline CVD graphene is comparable to pristine graphene.<sup>58</sup> Jin et al. and Dulbak et al. reported that sputter deposition induced disorder and damaged graphene,<sup>59,60</sup> therefore it is not a priori known whether Gr can withstand the rough conditions during thermal metal deposition.

To test the mechanical stability of the graphene layer during metal deposition, we deposited metal onto suspended graphene to investigate if the graphene can withstand the impact of the metal atoms and clusters during metal evaporation. By using suspended graphene, we use the worst case scenario where nothing is supporting the graphene layer during metal deposition (Figure 4a). We transferred single layer graphene on an array of holes  $(20 \times 20 \ \mu m)$  with a diameter of 100 nm in silicon nitride (Figure 4c). Subsequently, we deposited Au by thermal evaporation at a rate of 0.2-0.3 Å/s (at a base pressure of <5  $\times$  10<sup>-7</sup> mbar). Figure 4 shows the scanning electron microscopy (SEM) images of the Gr on the Si<sub>3</sub>N<sub>4</sub> membrane before (Figure 4c) and after metal deposition (Figure 4e). As described earlier, some PMMA residues on Gr from the transfer process are still present<sup>47</sup> and are used as markers for locating the same device area after Au deposition (Figure S1; see the Supporting Information) The contrast of the SEM images of the pattern in Si<sub>3</sub>N<sub>4</sub> increases because the conductive nature of Gr avoids charging (Figure 4c). Although PMMA residues are

**Figure 4.** (a) Schematic of the suspended graphene experiment. Au (30 nm) was evaporated onto graphene suspended over 100 nm diameter holes lithographically patterned in silicon nitride. Scanning electron micrographs of the 100 nm diameter holes in  $Si_3N_{42}$ , without (b) and with Gr (c). SEM images after the deposition of 30 nm of gold on the holes without (d) and covered with Gr (e).

#### **ACS Applied Materials & Interfaces**

present on the Gr film from the transfer process, we do not expect that they affect the mechanical strength of Gr due to very low stiffness and strength of PMMA.<sup>58</sup>

Figure 4e shows that the metal film is smooth, which indicates that the layer of Gr is not damaged during metal deposition. As a control, we also imaged an area of the membrane that was not covered with graphene (on the same sample) from which we conclude that the metal penetrated the holes (only about 5% of the holes clogged likely because of dust particles or process residues) and that the metal itself did not clog up all the holes. Hence, the suspended graphene is robust enough to withstand the impact from clusters of gold atoms<sup>61,62</sup> during metal deposition and withstands the high temperature differences (melting point of gold is 1064 °C and typical deposition temperatures are about 1800 °C).<sup>61</sup>

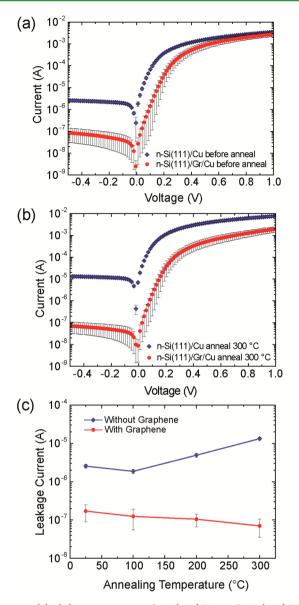

Thermal Stability. As mentioned earlier, many fabrication steps require elevated temperatures at which besides Cu diffusion also the formation of Cu<sub>3</sub>Si is an issue.<sup>63</sup> To investigate the thermal stability of the junctions, we followed the thermal stability by measuring the I(V) curves as a function of annealing temperature. Figure 5 shows the I(V) measurements of the n-Si(111)/Cu and n-Si(111)/Gr/Cu junctions before and after annealing at 100, 200, and 300 °C for 1 h. We fitted the forward bias current with the thermionic emission model (eq 1) as described above to extract the  $\phi_{\rm B}$  and *n*. Plotting the leakage current  $(I_s)$  of the *n*-Si(111)/Cu and *n*-Si(111)/Gr/Cu junctions at -0.5 V against the annealing temperature (Figure 5c) shows an increase of  $I_{\rm S}$  for the unprotected n-Si(111)/Cu devices, which started to degrade when heated above 100 °C. Remarkably, the value of  $I_s$ decreased for n-Si(111)/Gr/Cu devices, suggesting that the device properties improved after thermal stressing.

Table 1 lists the values of the Schottky barrier heights and ideality factors obtained by eq 1 following the same procedure as described above. We also determined the series resistance of the diodes ( $R_{series}$ ) for n-Si(111)/Cu and n-Si(111)/Gr/Cu devices before and after thermal stressing by using the modified thermionic emission model (eq 3) to include the combination of a resistor with resistance  $R_{series}$  and the diode through which the current I flows.<sup>64</sup> The voltage  $V_D$  across the diode is expressed in terms of the total voltage drop across the resistor and the diode. Using  $V_D = V - IR_{series}$ , and for  $V_D > 3kT/q$ , eq 1 becomes

$$I \approx I_{\rm s} \left[ \exp \left( \frac{q(V - IR_{\rm series})}{nkT} \right) \right]$$

(3)

Table 1 shows that  $R_{\text{series}}$  decreased, but the values of  $\phi_{\text{B}}$  decreased and *n* increased when we subjected the *n*-Si(111)/Cu devices to thermal stressing above 200 °C. We attribute the decrease of  $\phi_{\text{B}}$  and increase of *n* to the formation of Cu<sub>3</sub>Si alloy because of interfacial reaction between Cu and Si (see below for details).<sup>62</sup> We attribute the decrease in  $R_{\text{series}}$  to Si doping by Cu diffusion at low temperature (100 °C) and the formation of the Cu<sub>3</sub>Si at elevated temperatures (>200 °C; see below). It has been reported before that Cu<sub>3</sub>Si formation in Si nanowires reduces the resistance of Si due to doping<sup>65</sup> and we propose that a similar mechanism exists in our *n*-Si(111)/Cu devices to decrease  $R_{\text{series}}$ . The formation of Cu<sub>3</sub>Si could also result in an increase in the effective contact area due to the formation of spikes<sup>6</sup> at the interface, resulting in an increase in the currents at both reverse and forward bias.

**Figure 5.** (a) I(V) measurements of *n*-Si(111)/Cu and *n*-Si(111)/Gr/Cu before annealing and (b) after annealing at 300 °C for 1 h. (c) Reverse saturation current  $I_s$  at -0.5 V plotted against the annealing temperature for Si/Cu and Si/Gr/Cu devices.

For the *n*-Si(111)/Gr/Cu devices, the values of  $\phi_B$  and *n* remained unchanged after annealing up to 300 °C for 1h showing that the devices remained intact after thermal stressing. The reverse saturation current of *n*-Si(111)/Gr/Cu devices decreased, which indicates that these junctions improved in their performance. The decrease of  $R_{\text{series}}$  could be due to improved contacts of the Gr with the Si and/or Cu layers.

Although the  $\phi_{\rm B}$  of *n*-Si(111)/Gr/Cu devices have higher barrier heights than the unprotected *n*-Si(111)/Cu devices, we explain that due to the high diffusivity of Cu in Si, the asdeposited *n*-Si(111)/Cu devices are doped by Cu and have a reduced barrier height because of the formation of Cu related defect states at the interface. This effect is also evident in the reduction in ideality factor from n = 1.57 of the *n*-Si(111)/Cu devices to n = 1.13 of the *n*-Si(111)/Gr/Cu devices.

Silicide Formation. In the previous section, we inferred that silicides are formed at elevated temperatures. We used

#### **Research Article**

|                            | <i>n-</i> Si(111)/Cu |                   |                              | <i>n</i> -Si(111)/Gr/Cu |                          |                              |

|----------------------------|----------------------|-------------------|------------------------------|-------------------------|--------------------------|------------------------------|

| annealing temperature (°C) | barrier height (eV)  | ideality factor n | series resistance $(\Omega)$ | barrier height (eV)     | ideality factor <i>n</i> | series resistance $(\Omega)$ |

| RT                         | $0.567 \pm 0.004$    | $1.57 \pm 0.06$   | $261 \pm 17$                 | $0.70 \pm 0.05$         | $1.13 \pm 0.11$          | 546 ± 124                    |

| 100                        | $0.570 \pm 0.010$    | $1.58 \pm 0.19$   | $188 \pm 60$                 | $0.72 \pm 0.03$         | $1.08 \pm 0.02$          | $500 \pm 109$                |

| 200                        | $0.539 \pm 0.003$    | $1.96 \pm 0.11$   | $185 \pm 14$                 | $0.70 \pm 0.03$         | $1.11 \pm 0.04$          | 286 ± 65                     |

| 300                        | $0.515 \pm 0.002$    | $2.05 \pm 0.07$   | 134 ± 16                     | $0.69 \pm 0.02$         | $1.14 \pm 0.07$          | 311 ± 64                     |

|                            | (a)                  |                   | (b)                          |                         |                          |                              |

|                            | n-Si(111)/Cu         | n-Si(111)/Gr/     | Cu                           |                         |                          |                              |

Table 1. Electrical Properties of the *n*-Si(111)/Cu and *n*-Si(111)/Gr/Cu Junctions vs Temperature

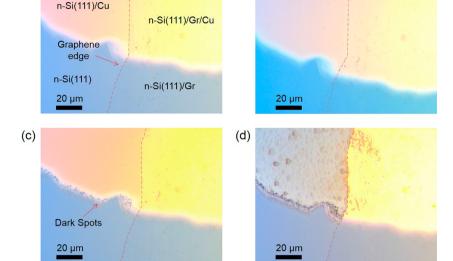

Figure 6. Optical micrographs of a boundary of *n*-Si(111)/Gr/Cu and *n*-Si(111)/Cu devices at room temperature (a), and after thermal stressing in high vacuum for 1 h at 100 °C (b), 200 °C (c), and 300 °C (d).

optical microscopy and X-ray diffraction (XRD) to follow silicide formation. Figures 6 and 7 show the optical images and X-ray diffractograms of the devices before and after thermal stressing, respectively. Figure 6 shows the optical micrographs of the boundary between the protected *n*-Si(111)/Gr/Cu and unprotected *n*-Si(111)/Cu as a function of temperature. Annealing at 200 °C for 1 h results in the appearance of dark spots (Figure 6c) and annealing at 300 °C for 1 h (Figure 6d) results in a complete change in surface morphology. The graphene protected areas remained unchanged over the course of thermal annealing except for some lateral diffusion of Cu<sub>3</sub>Si into Cu film in Figure 5d.

To confirm the formation of Cu<sub>3</sub>Si, we performed X-ray diffraction (XRD) of the unprotected *n*-Si(111)/Cu and the protected *n*-Si(111)/Cu interfaces. Figure 7 shows the X-ray diffractograms of  $2\theta$  against intensity of the as-deposited *n*-Si(111)/Cu and *n*-Si(111)/Gr/Cu devices before and after annealing at 200 and 300 °C for 1 h. The formation of Cu<sub>3</sub>Si peaks (red lines, Figure 7) after annealing above 200 °C shows that the interface degraded due to interdiffusion and alloying of Cu and Si. The XRD spectra for protected *n*-Si(111)/Gr/Cu interface showed no alloying even after annealing up to 300 °C for 1 h.

Nguyen et al.<sup>30</sup> and Hong et al.<sup>31</sup> reported using trilayer and monolayer graphene as a Cu diffusion barrier respectively and showed that graphene prevented the diffusion of Cu into Si up to annealing at 700 °C for 30 min. Our results using monolayer graphene supports their conclusion that graphene functions as an effective diffusion barrier for use in Cu metallization and we further show that Gr is an electronically transparent barrier and does not change the energetics of the interface. We did not anneal the *n*-Si(111)/Gr/Cu beyond 300 °C but we expect similar barrier behavior as observed by Hong et al.,<sup>31</sup> as they used a similar CVD graphene.

## CONCLUSIONS

Here we show that graphene is electronically transparent when sandwiched between silicon and Au or Cu. Both Au and Cu do not penetrate the graphene barrier during the direct evaporation step or by diffusion even during thermal stressing. We studied the *n*-Si(111)/Gr/Au interface by BEEM ( $\sim 1 \text{ nm}^2$ spatial resolution) and showed that there is no direct contact between *n*-Si(111) and Au at the nanoscale and the *n*-Si(111)/ Gr/Au barrier height remains unchanged. Remarkably, thermal stressing at 300 °C for 1 h reduced the contact resistance and lowered the leakage currents across the diodes. In other words, thermal stressing resulted in a measurable improvement of the diode characteristics. In addition, the Gr layer also prevented the formation of silicides. The layer of Gr introduced negligible resistance and is therefore "electronically transparent". Thus, our results show that atomically thin Gr is a promising material to protect interfaces (i) it does not introduce significant resistances, (ii) it is chemically and mechanically stable during the fabrication process, and (iii) it blocks unwanted doping. Currently, we are investigating how the number of Gr layers affect the junction properties.

Figure 7. XRD spectra of (a) n-Si(111)/Cu before and after annealing at 200 and 300 °C for 1 h showing the formation of Cu<sub>3</sub>Si after annealing at 200 °C. (b) n-Si(111)/Gr/Cu before and after annealing at 200 and 300 °C.

#### ASSOCIATED CONTENT

#### **S** Supporting Information

Derivation of the simplified thermionic emission model (eq 1) and a scanning electron micrograph of the  $Si_3N_4$  membrane with the marked location of Figure 4e before Au deposition. This material is available free of charge via the Internet at http://pubs.acs.org.

# AUTHOR INFORMATION

#### **Corresponding Authors**

\*C.A.N. E-mail: christian.nijhuis@nus.edu.sg.

\*C.T. E-mail: cedric-t@imre.a-star.edu.sg.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This work is supported by the Singapore National Research Foundation under the NRF fellowship (NRF award no. NRF-RF2010-03) to C.A.N. and the NUS Chemistry–IMRE joint laboratories (Molecular Materials Lab) awarded to C.T. and C.A.N. We thank Jie Deng for the fabrication of  $Si_3N_4$ membranes and SEM imaging and Poh Chong Lim for performing the XRD measurements. C.P.Y.W. thanks Yuan Li and Baris Yavas for initial experiments.

#### REFERENCES

(1) Weber, E. R. Transition Metals in Silicon. *Appl. Phys. A: Mater. Sci. Process.* **1983**, 30, 1–22.

(2) Sze, S. M. *Physics of Semiconductor Devices*, 2nd ed; John Wiley & Sons: New York, 1981.

(3) Nicolet, M. A. Diffusion Barriers in Layered Contact Structures. J. Vac. Sci. Technol. 1981, 19, 786–793.

(4) Tsai, M. H.; Sun, S. C.; Tsai, C. E.; Chuang, S. H.; Chiu, H. T. Comparison of the Diffusion Barrier Properties of Chemical-Vapor-Deposited TaN and Sputtered TaN between Cu and Si. *J. Appl. Phys.* **1996**, *79*, 6932–6938.

(5) Baumann, J.; Werner, T.; Ehrlich, A.; Rennau, M.; Kaufmann, C.; Gessner, T. TiN Diffusion Barriers for Copper Metallization. *Microelectron. Eng.* **1997**, 37–38, 221–228.

(6) Baumann, J.; Kaufmann, C.; Rennau, M.; Werner, T.; Gessner, T. Investigation of Copper Metallization Induced Failure of Diode Structures With and Without a Barrier Layer. *Microelectron. Eng.* **1997**, *33*, 283–291.

(7) Holloway, K.; Fryer, P. M. Tantalum as a Diffusion Barrier between Copper and Silicon. *Appl. Phys. Lett.* **1990**, *57*, 1736–1738.

(8) Xie, Q.; Qu, X.-P.; Tan, J.-J.; Jiang, Y.-L.; Zhou, M.; Chen, T.; Ru, G.-P. Superior Thermal Stability of Ta/TaN Bi-layer Structure for Copper Metallization. *Appl. Surf. Sci.* **2006**, *253*, 1666–1672.

(9) Bohr, M. T. Interconnect Scaling - The Real Limiter to High Performance ULSI. In *International Electron Devices Meeting Proceedings*, Washington, DC, December 10–13, 1995; IEEE: New York, 1995; pp 241–244.

(10) Jeong, M.-I.; Park, S.-E.; Kim, D.-H.; Lee, J.-S.; Park, Y.-C.; Ahn, K.-S.; Choi, C.-J. Transmission Electron Microscope Study of Screen-Printed Ag Contacts on Crystalline Si Solar Cells. *J. Electrochem. Soc.* **2010**, *157*, H934–H936.

(11) Nason, T. C.; Yang, G. R.; Park, K. H.; Lu, T. M. Study of Silver Diffusion into Si(111) and SiO2 at Moderate Temperatures. *J. Appl. Phys.* **1991**, *70*, 1392–1396.

(12) Bunch, J. S.; Verbridge, S. S.; Alden, J. S.; van der Zande, A. M.; Parpia, J. M.; Craighead, H. G.; McEuen, P. L. Impermeable Atomic Membranes from Graphene Sheets. *Nano Lett.* **2008**, *8*, 2458–2462.

(13) Kim, H.-Y.; Lee, C.; Kim, J.; Ren, F.; Pearton, S. J. Graphene as a Diffusion Barrier for Al and Ni/Au Contacts on Silicon. *J. Vac. Sci. Technol., B* **2012**, *30*, 030602–4.

(14) Geim, A. K.; Novoselov, K. S. The Rise of Graphene. Nat. Mater. 2007, 6, 183–191.

(15) Cobas, E.; Friedman, A. L.; Van't Erve, O. M.; Robinson, J. T.; Jonker, B. T. Graphene as a Tunnel Barrier: Graphene-based Magnetic Tunnel Junctions. *Nano Lett.* **2012**, *12*, 3000–3004.

(16) van't Erve, O. M.; Friedman, A. L.; Cobas, E.; Li, C. H.; Robinson, J. T.; Jonker, B. T. Low-Resistance Spin Injection into Silicon using Graphene Tunnel Barriers. *Nat. Nanotechnol.* **2012**, *7*, 737–742.

(17) Lee, C.; Wei, X.; Kysar, J. W.; Hone, J. Measurement of the Elastic Properties and Intrinsic Strength of Monolayer Graphene. *Science* **2008**, *321*, 385–338.

(18) Balandin, A. A.; Ghosh, S.; Bao, W.; Calizo, I.; Teweldebrhan, D.; Miao, F.; Lau, C. N. Superior Thermal Conductivity of Single-Layer Graphene. *Nano Lett.* **2008**, *8*, 902–907.

(19) Liu, L.; Ryu, S.; Tomasik, M. R.; Stolyarova, E.; Jung, N.; Hybertsen, M. S.; Steigerwald, M. L.; Brus, L. E.; Flynn, G. W. Graphene Oxidation: Thickness-Dependent Etching and Strong Chemical Doping. *Nano Lett.* **2008**, *8*, 1965–11970.

(20) Kim, K.; Regan, W.; Geng, B.; Alemán, B.; Kessler, B. M.; Wang, F.; Crommie, M. F.; Zettl, A. High-Temperature Stability of Suspended Single-Layer Graphene. *Phys. Status Solidi RRL* **2010**, *4*, 302–304.

(21) Kapoor, A. K.; Thomas, M. E.; Ciacchella, J. F.; Hartnett, M. P. Tantalum Nitride-p-Silicon High-Voltage Schottky Diodes. *IEEE Trans. Electron Devices* **1988**, *35*, 1372–1377.

(22) Finetti, M.; Suni, I.; Bartur, M.; Banwell, T.; Nicolet, M. A. Schottky Barrier Height of Sputtered TiN Contacts on Silicon. *Solid-State Electron.* **1984**, *27*, 617–623.

(23) Meaden, G. T. *Electrical Resistance of Metals*; Plenum Press: New York, 1965.

(24) Chen, L.; Zeng, Y.; Nyugen, P.; Alford, T. L. Silver Diffusion and Defect Formation in Si (1 1 1) Substrate at Elevated Temperatures. *Mater. Chem. Phys.* **2002**, *76*, 224–227.

#### **ACS Applied Materials & Interfaces**

(25) Istratov, A.; Flink, C.; Hieslmair, H.; Weber, E.; Heiser, T. Intrinsic Diffusion Coefficient of Interstitial Copper in Silicon. *Phys. Rev. Lett.* **1998**, *81*, 1243–1246.

(26) Wilcox, W. R.; LaChapelle, T. J. Mechanism of Gold Diffusion into Silicon. J. Appl. Phys. **1964**, 35, 240–246.

(27) ITRS. International Technology Roadmap for Semiconductors, 2013, available via the internet at http://www.itrs.net.

(28) Kim, D.-k.; Lee, H.; Kim, D.; Keun Kim, Y. Electrical and Mechanical Properties of Tantalum Nitride Thin Films Deposited by Reactive Sputtering. *J. Cryst. Growth* **2005**, *283*, 404–408.

(29) Chung, H.; Chang, M.; Chu, S.; Kumar, N.; Goto, K.; Maity, N.; Sankaranarayanan, S.; Okamura, H.; Ohtsuka, N.; Ogawa, S. An Ultra-Thin ALD TaN Barrier for High-Performance Cu Interconnects. *IEEE Int. Symp. Semicond. Manuf. Conf.* **2003**, 454–456.

(30) Nguyen, B.-S.; Lin, J.-F.; Perng, D.-C. 1-nm-Thick Graphene Tri-Layer as the Ultimate Copper Diffusion Barrier. *Appl. Phys. Lett.* **2014**, *104*, 082105–5.

(31) Hong, J.; Lee, S.; Lee, S.; Han, H.; Mahata, C.; Yeon, H. W.; Koo, B.; Kim, S. I.; Nam, T.; Byun, K.; Min, B. W.; Kim, Y. W.; Kim, H.; Joo, Y. C.; Lee, T. Graphene as an Atomically Thin Barrier to Cu Diffusion into Si. *Nanoscale* **2014**, *6*, 7503–7511.

(32) Kaiser, W. J.; Bell, L. D. Direct Investigation of Subsurface Interface Electronic Structure by Ballistic-Electron-Emission Microscopy. *Phys. Rev. Lett.* **1988**, *60*, 1406–1409.

(33) Bell, L. D.; Kaiser, W. J. Observation of Interface Band Structure by Ballistic-Electron-Emission Microscopy. *Phys. Rev. Lett.* **1988**, *61*, 2368–2371.

(34) Chen, S.; Brown, L.; Levendorf, M.; Cai, W.; Ju, S. Y.; Edgeworth, J.; Li, X.; Magnuson, C. W.; Velamakanni, A.; Piner, R. D.; Kang, J.; Park, J.; Ruoff, R. S. Oxidation Resistance of Graphene-Coated Cu and Cu/Ni Alloy. *ACS Nano* **2011**, *5*, 1321–1327.

(35) Wang, G.; Kim, Y.; Choe, M.; Kim, T. W.; Lee, T. A New Approach for Molecular Electronic Junctions with a Multilayer Graphene Electrode. *Adv. Mater.* **2011**, *23*, 755–760.

(36) Maiti, U. N.; Lee, W. J.; Lee, J. M.; Oh, Y.; Kim, J. Y.; Kim, J. E.; Shim, J.; Han, T. H.; Kim, S. O. 25th Anniversary Article: Chemically Modified/Doped Carbon Nanotubes & Graphene for Optimized Nanostructures & Nanodevices. *Adv. Mater.* **2014**, *26*, 40–67.

(37) Nijhuis, C. A.; Reus, W. F.; Whitesides, G. M. Molecular Rectification in Metal-SAM-Metal Oxide-Metal Junctions. *J. Am. Chem. Soc.* **2009**, *131*, 17814–17827.

(38) Nijhuis, C. A.; Reus, W. F.; Whitesides, G. M. Mechanism of Rectification in Tunneling Junctions Based on Molecules with Asymmetric Potential Drops. *J. Am. Chem. Soc.* **2010**, *132*, 18386–18401.

(39) Nerngchamnong, N.; Yuan, L.; Qi, D. C.; Li, J.; Thompson, D.; Nijhuis, C. A. The Role of van der Waals Forces in the Performance of Molecular Diodes. *Nat. Nanotechnol.* **2013**, *8*, 113–118.

(40) Tung, R. T. The Physics and Chemistry of the Schottky Barrier Height. *Appl. Phys. Rev.* **2014**, *1*, 011304-1–011304-50.

(41) Higashi, G. S.; Chabal, Y. J.; Trucks, G. W.; Raghavachari, K. Ideal Hydrogen Termination of the Si (111) Surface. *Appl. Phys. Lett.* **1990**, *56*, 656–658.

(42) Li, X.; Zhu, Y.; Cai, W.; Borysiak, M.; Han, B.; Chen, D.; Piner, R. D.; Colombo, L.; Ruoff, R. S. Transfer of Large-Area Graphene Films for High-Performance Transparent Conductive Electrodes. *Nano Lett.* **2009**, *9*, 4359–4363.

(43) Goh, K. E.; Bannani, A.; Troadec, C. Imaging Buried Organic Islands by Spatially Resolved Ballistic Electron Emission Spectroscopy. *Nanotechnology* **2008**, *19*, 445718-1–445718-6.

(44) Leong, E. S. P.; Deng, J.; Liu, Y. J.; Teng, J. H. Dual Metamaterial Structures Generated from an One-Step Fabrication Using Stencil Lithography. *Appl. Phys. A: Mater. Sci. Process.* **2014**, 907–912.

(45) Ferrari, A. C.; Meyer, J. C.; Scardaci, V.; Casiraghi, C.; Lazzeri, M.; Mauri, F.; Piscanec, S.; Jiang, D.; Novoselov, K. S.; Roth, S.; Geim, A. K. Raman Spectrum of Graphene and Graphene Layers. *Phys. Rev. Lett.* **2006**, *97*, 187401-1–187401-4.

(46) Blake, P.; Hill, E. W.; Castro Neto, A. H.; Novoselov, K. S.; Jiang, D.; Yang, R.; Booth, T. J.; Geim, A. K. Making Graphene Visible. *Appl. Phys. Lett.* **200**7, *91*, 063124-1–063124-3.

(47) Pirkle, A.; Chan, J.; Venugopal, A.; Hinojos, D.; Magnuson, C. W.; McDonnell, S.; Colombo, L.; Vogel, E. M.; Ruoff, R. S.; Wallace, R. M. The Effect of Chemical Residues on the Physical and Electrical Properties of Chemical Vapor Deposited Graphene Transferred to SiO2. *Appl. Phys. Lett.* **2011**, *99*, 122108-1–122108-3.

(48) Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; Banerjee, S. K.; Colombo, L.; Ruoff, R. S. Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. *Science* **2009**, *324*, 1312–1314.

(49) Troadec, C.; Goh, K. E. J. Dual Parameter Ballistic Electron Emission Spectroscopy Analysis of Inhomogeneous Interfaces. J. Vac. Sci. Technol., B 2010, 28, CSF1–CSF4.

(50) Kim, D.-J.; Kim, G.-S.; Park, N.-W.; Lee, W.-Y.; Sim, Y.; Kim, K.-S.; Seong, M.-J.; Koh, J.-H.; Hong, C.-H.; Lee, S.-K. Effect of Annealing of Graphene Layer on Electrical Transport and Degradation of Au/Graphene/n-Type Silicon Schottky Diodes. *J. Alloys Compd.* **2014**, *612*, 265–272.

(51) Banerjee, T.; van der Wiel, W. G.; Jansen, R. Spin Injection and Perpendicular Spin Transport in Graphite Nanostructures. *Phys. Rev. B* **2010**, *81*, 214409-1–214409-6.

(52) Giovannetti, G.; Khomyakov, P. A.; Brocks, G.; Karpan, V. M.; van den Brink, J.; Kelly, P. J. Doping Graphene with Metal Contacts. *Phys. Rev. Lett.* **2008**, *101*, 026803-1–026803-4.

(53) Wallace, P. The Band Theory of Graphite. *Phys. Rev.* 1947, 71, 622-634.

(54) Malec, C. E.; Davidović, D. Electronic Properties of Au-Graphene Contacts. *Phys. Rev. B* **2011**, *84*, 033407-1–033407-4.

(55) Klusek, Z.; Dabrowski, P.; Kowalczyk, P.; Kozlowski, W.; Olejniczak, W.; Blake, P.; Szybowicz, M.; Runka, T. Graphene on Gold: Electron Density of States Studies by Scanning Tunneling Spectroscopy. *Appl. Phys. Lett.* **2009**, *95*, 113114-1–113114-3.

(56) Sutter, P.; Sadowski, J. T.; Sutter, E. Graphene on Pt(111): Growth and Substrate Interaction. *Phys. Rev. B* 2009, *80*, 245411-1–245411-10.

(57) Bardeen, J. Surface States and Rectification at a Metal Semi-Conductor Contact. *Phys. Rev.* **1947**, *71*, 717–727.

(58) Lee, G. H.; Cooper, R. C.; An, S. J.; Lee, S.; van der Zande, A.; Petrone, N.; Hammerberg, A. G.; Lee, C.; Crawford, B.; Oliver, W.; Kysar, J. W.; Hone, J. High-Strength Chemical-Vapor-Deposited Graphene and Grain Boundaries. *Science* **2013**, *340*, 1073–1076.

(59) Jin, Z.; Su, Y.; Chen, J.; Liu, X.; Wu, D. Study of AlN Dielectric Film on Graphene by Raman Microscopy. *Appl. Phys. Lett.* **2009**, *95*, 233110-1–233110-3.

(60) Dlubak, B.; Seneor, P.; Anane, A.; Barraud, C.; Deranlot, C.; Deneuve, D.; Servet, B.; Mattana, R.; Petroff, F.; Fert, A. Are  $Al_2O_3$  and MgO Tunnel Barriers Suitable for Spin Injection in Graphene? *Appl. Phys. Lett.* **2010**, *97*, 092502-1–092502-3.

(61) Beavitt, A. R.; Turnell, R. C.; Campbell, D. S. A Study of the Energy Distribution and Nucleation of Evaporated Gold Using a Velocity Selector. *Thin Solid Films* **1967**, *1*, 3–11.

(62) Barnes, M. C.; Kim, D.-Y.; Ahn, H. S.; Lee, C. O.; Hwang, N. M. Deposition Mechanism of Gold by Thermal Evaporation: Approach by Charged Cluster Model. *J. Cryst. Growth* **2000**, *213*, 83–92.

(63) Cros, A.; Aboelfotoh, M. O.; Tu, K. N. Formation, Oxidation, Electronic, and Electrical Properties of Copper Silicides. *J. Appl. Phys.* **1990**, *67*, 3328–3336.

(64) Cheung, S. K.; Cheung, N. W. Extraction of Schottky Diode Parameters from Forward Current-Voltage Characteristics. *Appl. Phys. Lett.* **1986**, *49*, 85–87.

(65) Johnson, D. C.; Mosby, J. M.; Riha, S. C.; Prieto, A. L. Synthesis of Copper Silicide Nanocrystallites Embedded in Silicon Nanowires for Enhanced Transport Properties. *J. Mater. Chem.* **2010**, *20*, 1993–1998.